Présentation

RÉSUMÉ

Cet article a pour but de retracer les évolutions techniques qui ont abouti aux mémoires actuelles. Après une brève présentation des différents sous-ensembles de ce composant que sont la matrice de mémorisation, la logique de contrôle et l’interface d’entrée-sortie, nous détaillons pour chacun d’eux leurs évolutions. Le portrait de ce que l’on pourrait appeler la « mémoire idéale » est ensuite esquissé à partir des recherches et des réponses industrielles actuelles. En particulier trois composants électroniques disponibles aujourd’hui qui sont les mémoires à changement de phase, ferroélectriques et magnétorésistives (respectivement la PCRAM, la FRAM et la MRAM) sont présentés.

Lire cet article issu d'une ressource documentaire complète, actualisée et validée par des comités scientifiques.

Lire l’articleAuteur(s)

-

Philippe DARCHE : Maître de conférences à l’institut universitaire de technologie (IUT) Paris Descartes - Chercheur au laboratoire LIP6 – université Pierre et Marie Curie (UPMC), France

INTRODUCTION

Depuis les premières mémoires intégrées vives statiques et dynamiques de la société Intel apparues respectivement en 1969 et 1971, ce composant n’a cessé d’évoluer en termes de capacité de stockage et de performance, principalement le temps de latence et le débit. La capacité de la mémoire dynamique est ainsi passée de 1 Kib (référence Intel 1103 - 1971) à 8 Gib (DDR3 SDRAM - 2012) et son temps de cycle a débuté à 580 ns pour arriver aux alentours de 40 ns (modèle 1600 9-9-9-24, ligne activée) pour une lecture aléatoire (mêmes références que précédemment).

L’objet de cet article est de retracer les évolutions techniques de la mémoire à semi-conducteurs. Les différents sous-ensembles de ce composant, qui sont la matrice de mémorisation, la logique de contrôle périphérique et l’interface, sont d’abord présentés. Nous détaillons ensuite l’évolution de chacun d’eux. Par ailleurs les progrès de l’intégration font qu’il est aujourd’hui possible d’intégrer un système informatique sur une seule puce. La mémoire qui y est intégrée se nomme mémoire embarquée. Nous précisons ses avantages. Pour terminer, nous esquissons ce que pourrait être la « mémoire idéale » à partir des recherches actuelles. Son portrait pourrait être une capacité de stockage identique à celle des mémoires « classiques », une absence de volatilité de l’information, un débit compatible avec les architectures de processeurs actuelles et une meilleure efficacité énergétique. Nous présentons en particulier trois réponses industrielles actuelles que sont les mémoires à changement de phase, ferroélectriques et magnétorésistives dont les représentants respectifs sont la PCRAM, la FRAM et la MRAM.

MOTS-CLÉS

technologie de l'information mémoire à semi-conducteurs à accès aléatoire mémoire vive mémoire morte mémoire émergente

VERSIONS

- Version courante de juin 2020 par Philippe DARCHE

DOI (Digital Object Identifier)

CET ARTICLE SE TROUVE ÉGALEMENT DANS :

Accueil > Ressources documentaires > Archives > [Archives] Technologies logicielles et architecture des systèmes > Évolution des mémoires à semi-conducteurs à accès aléatoire > Évolution de la logique de contrôle

Présentation

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

3. Évolution de la logique de contrôle

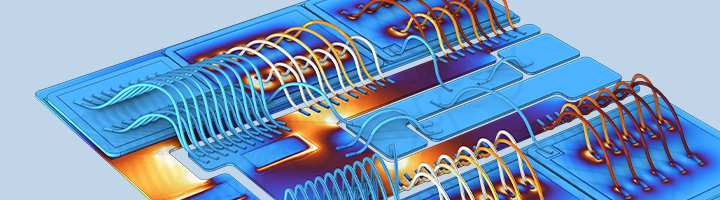

La logique de contrôle (figure 12), périphérique au plan de mémorisation, concerne principalement le décodeur d’adresse de ligne de mot, le conditionneur de ligne de bit, l’amplificateur de lecture SA, ainsi que le multiplexeur de colonnes (MUX). Ce dernier regroupe les fonctions de décodage d’adresse de colonne et de sélection d’une colonne.

3.1 Décodeur d’adresse de ligne

Le rôle des décodeurs d’adresse est de sélectionner une ligne et une colonne afin d’adresser par coïncidence la cellule de mémorisation. Pour cela, l’adresse fournie à la mémoire est décomposée en deux champs, l’adresse de ligne, de poids le plus élevé, et celle de colonne. Par ailleurs, il faut distinguer le décodeur d’adresse de ligne et celui de colonne. En effet, ce dernier, associé à un sélectionneur, est en fait un multiplexeur qui permet de faire circuler l’information binaire de ou vers la cellule.

Le décodeur d’adresse de ligne est chargé, à partir de l’adresse, d’activer une unique ligne. L’augmentation de la capacité de mémorisation a fait augmenter le degré des mintermes de son équation booléenne. Au niveau implémentation dans une technologie CMOS, cela implique des étages d’entrées avec un nombre élevé de transistors en série qui entraîne une dégradation des temps de commutation qui sont proportionnels à l’entrance des portes. La solution usuellement retenue pour minimiser le nombre d’entrées est de réaliser un décodage en deux étapes dénommées « prédécodage » et « décodage final » comme l’illustre la figure 13. Une autre fonction est l’amplification électrique car chacune de ses sorties voit une capacité de ligne élevée.

HAUT DE PAGE3.2 Amplificateur de lecture

L’amplificateur de lecture (SA) est l’élément critique de la mémoire, surtout pour la DRAM car il doit déterminer un niveau logique à partir d’une différence de tensions de l’ordre de la centaine de millivolts. Il doit donc être sensible, rapide et posséder un gain en tension élevé....

Évolution de la logique de contrôle

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

BIBLIOGRAPHIE

-

(1) - DARCHE (P.) - Architecture des ordinateurs-Mémoires à semi-conducteurs : Principe de fonctionnement et organisation interne des mémoires vives. - Volume 1. Éditions Vuibert. ISBN 978-2-311-00476-2 (2012).

-

(2) - SIDDIQI (M.A.) - Dynamic RAM : Technology Advancements. - CRC Press. ISBN-13 978-1439893739 (2012).

-

(3) - Low power and reliable SRAM memory cell and array design. - Koichiro Ishibashi and Kenichi Osada Editors. Springer Series in Advanced Microelectronics. ISBN 978-3-642-19567-9 (2011).

-

(4) - MASUOKA (F.) et al - A new flash E2PROM cell using triple polysilicon technology. - 1984 International Electron Devices Meeting (IEDM) Digest, vol. 30, p. 464-467. December 1984.

-

(5) - DARCHE (P.) - Architecture des ordinateurs – Interfaces et périphériques-Cours avec exercices corrigés. - Éditions Vuibert. ISBN 2-7117-4814-6 (2003).

-

...

DANS NOS BASES DOCUMENTAIRES

ANNEXES

IEEE Draft Standard for Prefixes for Binary Multiples. IEEE Std P1541/D5. The Institute of Electrical and Electronics Engineers. New York, USA. April 2002.

IEEE Standard for Prefixes for Binary Multiples. IEEE Std 1541-2002. ISBN 0-7381-3386-8.

IEC Letter symbols to be used in electrical technology-Part 2 : Telecommunications and electronics-Symboles littéraux à utiliser en électrotechnique – Partie 2 : Télécommunications et électronique. International Electrotechnical Commission. IEC 60027-2 – Édition 2.0 – Bilingual. November 2000.

HAUT DE PAGEArticle inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.