Présentation

RÉSUMÉ

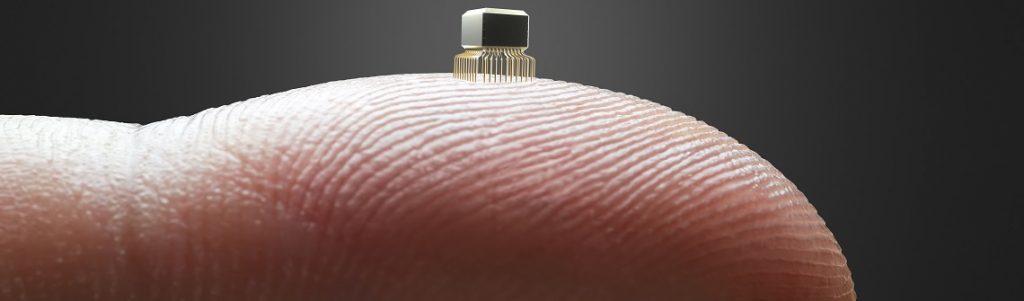

Dans la plupart des applications, la consommation d’énergie est un critère majeur dans la conception de circuits électroniques embarqués. Les contraintes sont de concevoir des systèmes à faible consommation de puissance ou à température maîtrisée, voire une combinaison des deux pour certains systèmes. Les applications mobiles ou embarquées alimentées sur piles ou batterie tombent dans le premier type d’application. Le deuxième type d’application implique des circuits complexes, intégrant un grand nombre de transistors (traitement multimédia, jeux vidéo…). Pour ces systèmes, différentes techniques au niveau matériel sont utilisées pour contrôler et réduire la puissance dissipée dans un circuit. Cet article propose un aperçu de ces techniques en se plaçant au niveau de l’architecture système.

Lire cet article issu d'une ressource documentaire complète, actualisée et validée par des comités scientifiques.

Lire l’articleAuteur(s)

-

Michel AUGUIN : Directeur de Recherche - Université Nice Sophia-Antipolis, CNRS, affecté au LEAT, Sophia-Antipolis, France.

-

François VERDIER : Professeur des Universités - Université Nice Sophia-Antipolis, CNRS, affecté au LEAT, Sophia-Antipolis, France.

-

Hend AFFES : Attachée Temporaire d’Enseignement et de Recherche - Université Nice Sophia-Antipolis, CNRS, affecté au LEAT, Sophia-Antipolis, France.

INTRODUCTION

Alors que les applications ne cessent d’évoluer vers plus de complexité, on assiste dans le même temps à un accroissement des difficultés à exploiter les avancées de la technologie des semi-conducteurs qui visent à apporter des solutions performantes à ces applications. Par exemple, sous l’appellation Internet des Objets au sens large (IoT), tout un ensemble de systèmes ou d’applications embarquées est envisagé avec un développement commercial attendu a priori très important. Parmi ces systèmes, on peut citer ceux portés par la personne (smart wearables) qui incluent des capteurs, des éléments de communication, de mémorisation et de calcul avec une part de logiciel embarqué significative. Dans le domaine de la mobilité, les perspectives de systèmes qui s’appuient sur une adaptation dynamique (les systèmes identifiés avec le préfixe « Software-defined » comme « Software-defined network », « software-defined application ») visent à rendre l’infrastructure plus flexible dans son offre de services vis-à-vis d’utilisateurs mobiles. Le domaine de la réalité virtuelle est aussi un secteur en pleine évolution avec des applications potentiellement nombreuses qui nécessitent des puissances de calcul et de mémorisation intégrées importantes. L’évolution vers des résolutions d’affichage en ultra haute définition a un impact direct sur les puissances de calcul, les tailles mémoires et les débits de données que doivent supporter les architectures matérielles. Cette brève présentation du domaine des applications illustre pourquoi les besoins en électronique embarquée continuent de progresser. Ainsi la mobilité sous-jacente à tous ces systèmes met l’accent sur l’énergie nécessaire à leur fonctionnement sur un intervalle de temps sans recharge qui ne doit pas constituer une contrainte trop forte pour un usage normal de ces systèmes. Il s’agit ici souvent de rechercher des solutions d’architectures qui maximisent le rapport puissance de calcul par joule consommé afin de permettre une durée de fonctionnement correcte entre deux recharges de la batterie.

Par ailleurs, comme indiqué ci-dessus, la technologie des semi-conducteurs peine aujourd’hui à assurer une amélioration des caractéristiques des circuits suivant la même dynamique que celle observée depuis quarante ans (dynamique décrite par la Loi de Moore et ses variantes). Comme nous le montrons dans la suite, maximiser le rapport puissance de calcul par joule consommé n’est plus toujours suffisant, il peut être nécessaire de chercher également à maximiser le rapport puissance de calcul par watt consommé et ce principalement pour des questions de dissipation thermique. En effet, le caractère embarqué et mobile de certaines applications empêche d’intégrer des systèmes sophistiqués de dissipation de chaleur, il faut donc agir directement sur la source de chaleur pour éviter une montée en température qui pourrait altérer la fiabilité du système.

Nous illustrons dans la suite les principales techniques qui permettent de structurer l’architecture d’un circuit afin de pouvoir en contrôler la puissance dissipée. Ainsi structurer un circuit en domaines de puissance et en domaines d’horloge donne la possibilité d’agir sur les paramètres qui impactent directement la consommation de puissance. Cependant, cette structuration modifie les comportements du circuit et peut conduire à introduire des erreurs logiques ou des altérations des comportements temporels. Ces différents points sont abordés dans la suite de l’article en se plaçant au niveau de l’architecture matérielle du système et sans détailler comment les techniques utilisées sont mises en œuvre au niveau logique ou technologique.

DOI (Digital Object Identifier)

Présentation

Article inclus dans l'offre

"Technologies logicielles Architectures des systèmes"

(236 articles)

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

5. Conclusion et perspectives

Les techniques matérielles pour supporter la mise en œuvre d’une gestion de puissance consommée dans les circuits électroniques embarqués sont diverses et localement efficaces. Pour atteindre une réelle efficacité énergétique, plusieurs difficultés sont à aborder :

-

L’organisation d’une architecture fonctionnelle suivant une structure de gestion de puissance doit être pensée dans sa globalité ;

Par exemple, insérer localement une multitude de mécanismes de contrôle de puissance peut devenir contre-productif de par la difficulté ensuite à les gérer efficacement au niveau système.

-

L’insertion de mécanismes de gestion de puissance affecte les performances fonctionnelles et peut également conduire à des erreurs logiques si toutes les précautions ne sont pas prises. La vérification fonctionnelle est ainsi complexifiée pour un circuit optimisé en consommation ;

-

L’optimisation conjointe des deux composantes statique et dynamique qui contribuent à la puissance consommée nécessite souvent des compromis qui dépendent des exigences au niveau système et des comportements fonctionnels ;

Par exemple, pour un circuit intégré dans un capteur qui est très souvent dans un état inactif et reste peu de temps en état actif, il peut s’agir d’optimiser principalement la puissance statique.

Dans un circuit complexe supportant des traitements intensifs, les deux sources de puissance consommée doivent être optimisées en prenant en compte l’activité fonctionnelle ;

Par exemple, suivant les courants de fuite, il peut être préférable de fonctionner à fréquence maximum pendant un intervalle de temps bref puis d’activer un contrôle de puissance (power gating) plutôt que d’activer le DVFS. Cette question se pose également pour des questions thermiques.

-

Si, au niveau matériel des mécanismes de contrôle de puissance consommée existent, il reste à les exploiter efficacement par les couches logicielles. Si le niveau applicatif est rarement impliqué dans la gestion de puissance, il n’en est pas de même des couches de l’intergiciel, système d’exploitation et logiciel dépendant matériel (firmware). Classiquement, plus ces couches sont proches du niveau applicatif, plus elles sont développées...

Conclusion et perspectives

Article inclus dans l'offre

"Technologies logicielles Architectures des systèmes"

(236 articles)

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

BIBLIOGRAPHIE

-

(1) - MAYO (R.N.), RANGANATHAN (P.) - Energy consumption in mobile devices: why future systems need requirements-aware energy scale-down. - HP Laboratories Palo Alto, HPL-2003-167 (2003).

-

(2) - SHAULY (E.N.) - CMOS Leakage and power reduction in transistors and circuits: process and layout considerations. - Journal of Low Power Electronics and Application (2012).

-

(3) - AGARWAL (A.) et al - Leakage Power Analysis and Reduction for Nanoscale Circuits. - IEEE Micro, Volume 26, Issue 2, March-April (2006).

-

(4) - JULIEN (N.) - Energie et puissance dans les systèmes embarqués. - Techniques de l’Ingénieur [H8260], 10 février (2015).

-

(5) - KAHNG (A.B.) - The ITRS Design Technology and System Drivers Roadmap: Process and Status. - Design Automation Conference, 29 Mai – 7 Juin, Austin, Texas, USA (2013).

-

...

ITRS, International Technology Roadmap for Semiconductors, ITRS Reports : http://www.itrs2.net/itrs-reports.html (2011 Edition, System Drivers, 2012 Update Overview)

Standard IEEE 1801-2015 UPF, https://standards.ieee.org/findstds/standard/1801-2015.html

Site CATRENE : Cluster for Application and Technology Research in Europe on NanoElectronics, http://www.catrene.org/

Site Si2, Silicon Integration Initiative, http://www.si2.org/ et le programme OpenStandard low power : https://projects.si2.org/lpc_index.php

Site de Texas Instrument https://www.ti.com/lit/pdf et notamment l’article de Loc Truong : Power Management in Embedded Systems with dual OSes : http://www.ti.com/lit/pdf/spry166

HAUT DE PAGE

IEEE Unified Power Format (UPF) for Design and Verification of Low-Power, Energy-Aware Electronic Systems, Standard IEEE 1801, 2015.

Des extensions à la norme IP-XACT IEEE 1685™-2009 pour décrire une structure de gestion de puissance au niveau RTL a été proposée : http://accellera.org/news/press-releases/107-accellera-systems-initiative-enhances-ip-xact-standard-with-new-vendor-extensions-for-analog-mixed-signal-and-low-power-designs

Site...

Article inclus dans l'offre

"Technologies logicielles Architectures des systèmes"

(236 articles)

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.