Présentation

RÉSUMÉ

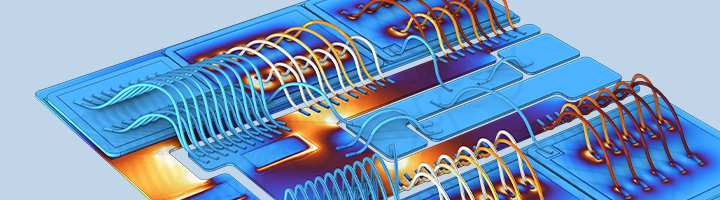

Cet article traite des méthodes de simulation des circuits électroniques. Suite à l’accroissement des tailles de circuits, ces méthodes répondent aux problématiques de précision tout en améliorant la rentabilité. L’analyse de bruit transitoire est destinée à étudier les perturbations sur des blocs tels que des PLL. Les analyses électrothermiques et le vieillissement se préoccupent de la fiabilité et la robustesse du circuit, tandis que les analyses de Monte-Carlo et de sensibilité s’attachent à évaluer les effets de dispersion des paramètres. La complexité des circuits devenant critique, des méthodes permettant d’augmenter les performances, en vitesse et en capacité des simulateurs sont aussi présentées.

Lire cet article issu d'une ressource documentaire complète, actualisée et validée par des comités scientifiques.

Lire l’articleAuteur(s)

-

Pascal BOLCATO : Engineering director, Analog and RF Simulation - Siemens Electronic Design Automation, Montbonnot, France

-

Dezaï GLAO : Principal engineer, Analog and mixed-signal Simulation - Siemens Electronic Design Automation, Montbonnot, France

-

Xavier JONSSON : R&D engineer, Specialist Statistics and Optimization - Siemens Electronic Design Automation, Montbonnot, France

INTRODUCTION

Le marché des puces électroniques continue sa forte expansion du fait de l’augmentation entre autres, de la demande pour des dispositifs électroniques de communication, des moyens de transports autonomes, des objets connectés, du traitement des donnés en masse (big data) et de l’internet des objets.

Cette demande a conduit, pendant des décennies, à une course à la miniaturisation des transistors qui a eu, pour effets bénéfiques, une augmentation des puissances de calcul tout en réduisant la taille, la consommation et les coûts unitaires dans un cercle vertueux entraînant investissements et fortes rentabilités. Cependant, la poursuite de cette stratégie agressive de réduction d’échelle et particulièrement la descente dans les dimensions nanométriques, révèlent de nouveaux défis et poussent les outils de conception et de vérification à se réinventer. Les tailles des circuits à simuler, compte tenu de l’augmentation du nombre de composants et des interconnexions, deviennent critiques. Les densités surfaciques de puissances dissipées deviennent si importantes, que leurs impacts sur le fonctionnement des dispositifs et leur durée de vie doivent être efficacement pris en compte. Cela est vrai pour toutes les applications de l’électronique, mais reste un sujet sensible particulièrement dans les applications des transports, du médical ou du militaire, pour lesquelles la fiabilité est un facteur de premier ordre. De même, la sensibilité aux variations des process de fabrication devient si importante que sa prise en compte est un facteur clé pour la réduction des coûts de production. Un autre effet de la descente dans les dimensions nanométriques est celui de l’augmentation de façon drastique des coûts de production, compte tenu de la complexité des procédés de fabrication eux-mêmes, poussant les industriels à investir en masse dans les unités de production, dans le but de réduire les coûts unitaires.

C’est dans ce contexte que cet article vient exposer comment le simulateur AMS/RF, présent aussi bien dans les phases de conception que dans celles de vérification des circuits, est un facteur déterminant sur le plan économique, pour réduire les temps de mise sur le marché et pour garantir la robustesse et la fiabilité, tout en améliorant les rendements de production. Cet article s’intéresse donc aux méthodes d’accélération des performances du simulateur AMS/RF, puis aux méthodes statistiques d’analyse de la variabilité du process, et finalement aux méthodes permettant d’obtenir une conception de circuits fiables et robustes. De l’efficacité de ces méthodes dépend en partie la possibilité de pouvoir continuer la miniaturisation qui augmente les performances tout en baissant la consommation et les prix de revient unitaires.

Le lecteur trouvera en fin d’article un glossaire et un tableau des sigles utilisés.

DOI (Digital Object Identifier)

Présentation

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.

BIBLIOGRAPHIE

-

(1) - ROHER (R.), NAGEL (L.), MEYER (R.), WEBER (L.) - Computationally efficient electronic circuit noise calculations. - IEEE J. Solid-State Circuits, vol. SC-6 (1971).

-

(2) - TELICHEVESKY (R.), KUNDERT (K.), WHITE (J.) - Efficient AC and noise analysis of two-tone RF circuits. - In Proc. IEEE DAC, p. 292-297 (1996).

-

(3) - ROYCHOWDHURY (J.), LONG (D.), FELDMANN (P.) - Cyclostationary noise analysis of large RF circuits with multitone excitations. - IEEE Journal of Solid-State Circuits, vol. 33, n° 3, p. 324-336 (1998).

-

(4) - BOLCATO (P.), NALLATAMBY (J.C.), LARCHEVÈQUE (R.), PRIGENT (M.), OBREGON (J.) - Unified approach of PM noise calculation in large RF multitone autonomous circuits. - IEEE MTT-S International Microwave Symposium Digest, vol. 1, p. 417-420 (2000).

-

(5) - BOLCATO (P.), TAWFIK (M.S.), POUJOIS (R.), JARRON (P.) - A new efficient transient noise analysis technique for simulation of CCD image sensors or particle detectors. - Proceedings of IEEE Custom Integrated Circuits...

DANS NOS BASES DOCUMENTAIRES

ANNEXES

1.1 Constructeurs – Fournisseurs – Distributeurs (liste non exhaustive)

Siemens EDA (AFS, Eldo, Symphony)

Cadence (Spectre, Spectre-RF, Ultrasim, AMS Designer)

Synopsys (Hspice, Hsim/XA, AMS Discovery)

HAUT DE PAGE

Organismes, comités œuvrant pour la standardisation :

IEEE-IRDS : définition de la feuille de route pour la réduction de la taille des transistors.

IEEE : promotion de la connaissance dans le domaine de l'ingénierie électrique.

ACCELERA : standardisation des langages HDL (verilog, vhdl).

CMC : standardisation et promotion de l'utilisation et de l'implémentation des modèles « compacts » de composants.

AEC : Automotive Electronic Council. Définitions Standardisation des méthodes de qualification et de tests des dispositifs électroniques utilisés...

Article inclus dans l'offre

Actualisée et enrichie d’articles validés par nos comités scientifiques.

Quiz, médias, tableaux, formules, vidéos, etc.

Opérationnels et didactiques, pour garantir l'acquisition des compétences transverses.

Un ensemble de services exclusifs en complément des ressources.